2.5Dパッケージが2020年代のIntel CPUの鍵となる革新的な積層技術

こんにちは、ライターのYUKOです。2020年代のIntel CPUの鍵となる革新的な積層技術である2.5Dパッケージについてお伝えします。

IntelのODI:2.5D積層技術の新たなフロンティア

Intelの新しい2.5D積層技術の帯域密度と伝送エナジーの目標は?

帯域密度:1TB/平方mm、伝送エナジー:0.1pJ/bit

Intelは、2.5Dおよび3D積層技術の新しいアプローチであるODIを発表しました。

ODIは、EMIBの代替として使用できますが、より高い帯域密度とより低い伝送エナジーを必要とするアプリケーションをサポートすることを目的としています。

ODIでは、ダイレクトなダイ同士の接続により、1TB/平方mmの垂直伝送帯域密度と0.1pJ/bitの伝送エナジーを実現できます。

これにより、TSVインタポーザやEMIBでは実現できない性能を、低いコストとより容易な排熱で実現できます。

Intelはまた、インターコネクトのバンプピッチを狭めて面積当たりの帯域密度を高める方向も示しました。

詳しくみる ⇒参照元: 2020年代のIntel CPUのカギとなる新2.5D/3D...パッケージングの未来:トランジスタ数1兆個

インテルがパッケージングの改善に向けて計画しているトランジスタ数の目標は?

1兆個

インテルはパッケージングの改善に注力しており、2030年までにパッケージ上のトランジスタ数を1,000億個から1兆個に増やすことを目指している。

これにより、超高密度・高性能が実現される見込みだ。

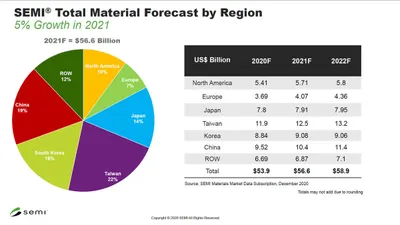

半導体パッケージング市場では、ASE Group、Amkor Technology、Samsung Electronics、Siliconware Precision Industriesなどの企業がリーダーシップを発揮している。

詳しくみる ⇒参照元: 2.5d 3d半導体パッケージの市場規模とシェア分析 -産業...チップの未来: Intelの3D統合ビジョン

Intelが計画している新しいボンディング技術は何?

ハイブリッドボンディング

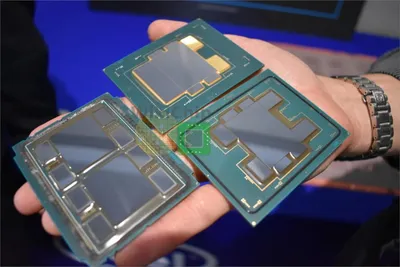

Intelは、より密接なチップレット間の垂直結合を実現するために、バンプピッチを20μmピッチ以下に縮小しようとしており、そのために「ハイブリッドボンディング」を導入する計画です。

この技術では、カッパーディッシュを使用してバンプピッチをさらに縮小し、ダイ・ツー・ウェハ、ウェハ・ツー・ウェハの工程に移行します。

これにより、チップはチップレットが密に貼り合わされ、パッケージとも密に結合されたものになります。

また、Intelはダイ内のトランジスタについても3D化を進めており、ダイの外側と内側を同時に積層化することで、チップの姿を根本的に変えようとしています。

詳しくみる ⇒参照元: 2020年代のIntel CPUのカギとなる新2.5D/3D...半導体パッケージングの技術

半導体チップの信号を外部に送信するために必要なバンプ形成の2つの種類は?

ファンイン、ファンアウト

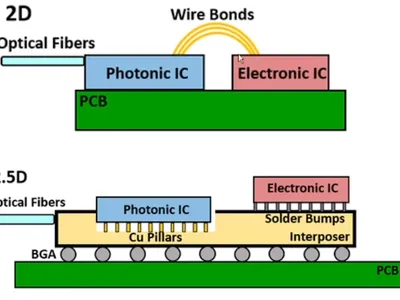

半導体チップの信号を外部に送信するために必要なバンプ形成には、チップの面積内で形成する「ファンイン」と、チップよりも大きな面積で形成する「ファンアウト」の2種類があります。

I/Oカウント(入力/出力数)が小さい場合はファンイン、大きい場合はファンアウトのパッケージング工程を行います。

ファンアウトでは、再配線層(RDL)も必要になります。

詳しくみる ⇒参照元: 半導体製造の8つの工程(8) 半導体を完成させる最後の手順「...半導体パッケージング市場の成長要因と課題

市場の抑制要因となっているのは何か?

半導体ICの設計

半導体業界は、コンシューマーエレクトロニクス用途の市場拡大により牽引されており、2.5D/3Dパッケージング技術が競争力を高める上で重要な役割を果たしています。

しかし、半導体ICの設計は複雑で初期投資が高いため、市場の抑制要因となっています。

COVID-19パンデミックによる半導体不足により、SMICなどのプレイヤーは生産能力の増強に注力しており、研究対象市場に恩恵がもたらされることが期待されています。

半導体デバイスの消費拡大は、デジタル化の進展、リモートワークの増加、電子機器の需要の高まりによって促進されており、先進的なパッケージング技術が、必要なフォームファクターと処理能力を提供しています。

2.5Dおよび3Dパッケージング技術は、3D統合による異種SoC設計の柔軟性など、その利点から急速に人気を集めています。

コンシューマーエレクトロニクスは、半導体ベンダーにとって重要なエンドユーザー業界です。

詳しくみる ⇒参照元: 市場調査レポート: 2.5dおよび3d半導体パッケージ市場-...EFB 2.5Dブリッジ技術の利点

EFB 2.5Dブリッジ技術によってAMDが得られる利点は?

基板の空洞化の回避

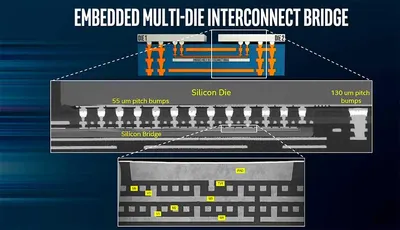

EFB 2.5Dブリッジ技術は、シリコンブリッジの空洞化に必要な有機パッケージ基板の複雑さとコストを削減します。

また、より優れた配置精度を実現し、リソグラフィー技術を使用して定義されたアーキテクチャを活用したウエハーレベルのプロセスを使用します。

さらに、標準的な基板やフリップチッププロセスを使用して、基板の製造、バンピング、組立工程での複雑さを軽減し、容量の問題を緩和します。

この技術は、「ムーアの法則を超える」スケーリングを可能にし、モノリシック設計では不可能な複雑なヘテロジニアスインテグレーションスキームに対応できます。

詳しくみる ⇒参照元: 先進パッケージング:ヘテロジニアスインテグレーションでムーア...2.5Dと3D半導体パッケージの市場動向

2.5Dと3Dの半導体パッケージはどのようなメリットがあるのか?

極めて高いパッケージング密度と高いエネルギー効率

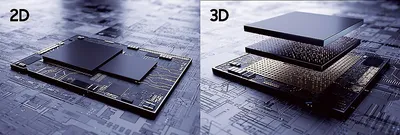

2.5Dと3Dの半導体パッケージは、極めて高いパッケージング密度と高いエネルギー効率を実現できるため、チップセット集積プラットフォームとして注目されています。

これにより、アクティブチップをダイスタッキングによって集積し、最短の相互接続と最小のパッケージフットプリントを実現できます。

本調査では、世界の2.5Dと3D半導体パッケージ製品の市場分析に重点が置かれ、市場サイジングはさまざまな市場プレーヤーが提供するパッケージングサービスを通じて生み出された収益を含んでいます。

地域別売上では、2.5Dと3Dパッケージング市場はサービス提供を扱っているため、数字は2.5Dと3Dパッケージングの供給を追跡しています。

市場は、パッケージング技術別、エンドユーザー産業別、地域別に区分され、市場規模と予測は金額(百万米ドル)ベースで提供されます。

詳しくみる ⇒参照元: 2.5d 3d半導体パッケージの市場規模とシェア分析 -産業...ODI: 3Dおよび2.5D統合技術

ODIの2つのバージョンである「キャビティ」バージョンと「カッパーピラー」バージョンでは、パッケージ基板とトップダイの間をどのように接続しているか?

型穴と銅ピラー

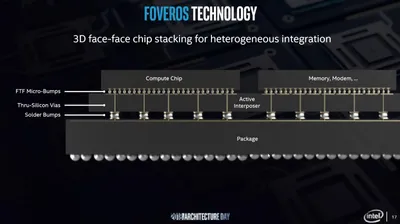

ODIには、「キャビティ」バージョンと「カッパーピラー」バージョンの2つの異なる技術があります。

キャビティバージョンでは、パッケージに型穴を開けてそこにベースダイを埋め込みます。

一方、カッパーピラーバージョンでは、パッケージ基板とトップダイの間を、高アスペクト比の銅の柱(ピラー)で接続します。

ODIのキャビティバージョンでは、ベースダイはTSVで垂直の配線を持っており、アクティブダイとして機能することもできます。

これにより、さまざまな2.5Dと3Dのバリエーションが可能となり、サブチップをメインプロセッサの下に埋め込む構成なども実現できます。

詳しくみる ⇒参照元: 2020年代のIntel CPUのカギとなる新2.5D/3D...先進パッケージング:ダイ間相互接続でイノベーションを加速する

チップレットパッケージアーキテクチャーは、どのようなものですか?

製品ごとの要件に基づいて選ばれる、特定の性能やコストに対応したアプローチ

チップレットパッケージアーキテクチャーは、特定の製品要件に合わせてカスタマイズされたアプローチです。

主な種類には、MCM、RDLベースのアーキテクチャー、シリコンベースのアーキテクチャー、3Dアクティブオンアクティブシリコンスタッキングなどがあります。

AMDは、2015年からHBMや2.5Dシリコンインターポーザ技術、MCMパッケージング、チップレットベースの技術など、さまざまなパッケージング技術を導入してきました。

これらの技術により、メモリ帯域幅の向上、コンピューティングパフォーマンスの向上、パフォーマンスと機能の向上などが実現されています。

詳しくみる ⇒参照元: 先進パッケージング:ヘテロジニアスインテグレーションでムーア...3Dパッケージング技術のメリットと未来

3Dパッケージング技術のメリットは?

ゲームパフォーマンスが15%向上

3Dパッケージング技術は、3Dチップレットテクノロジーを使用してアーキテクチャー全体のゲームパフォーマンスを15%向上させ、先進的なパッケージング技術の力を示しています。

また、技術的なコンピューティングワークロードでも同様のパフォーマンス上のメリットが得られます。

しかし、CPUコア上の3DキャッシュスタッキングはAMDの3Dパッケージ導入の段階に過ぎず、3Dスタッキングの未来にはTSVピッチの機能、IP-on-IPスタッキング、マクロオンマクロスタッキング、IPフォールディング/スプリット、回路レベルのスライシングなど、多くのアーキテクチャの革新があります。

詳しくみる ⇒参照元: 先進パッケージング:ヘテロジニアスインテグレーションでムーア...